# Computer Engineering

**Electrical Engineering Department Third Stage**

**Instructor: Asst. Lecturer**

Adnan Ali Abdullah

# EXTERNAL HARDWARE-INTERRUPT INTERFACE SIGNALS

# Minimum-Mode Interrupt Interface

#### ALE -O INT<sub>32</sub> M/IO -O INT<sub>33</sub> $\overline{RD}$ $\overline{WR}$ -O INT₃₄ External hardware 8086 AD<sub>0</sub>-AD<sub>15</sub> interrupt MPU interface circuitry INTR INTA $V_{CC}$ $DT/\overline{R}$ MN/MX DEN —O INT<sub>255</sub>

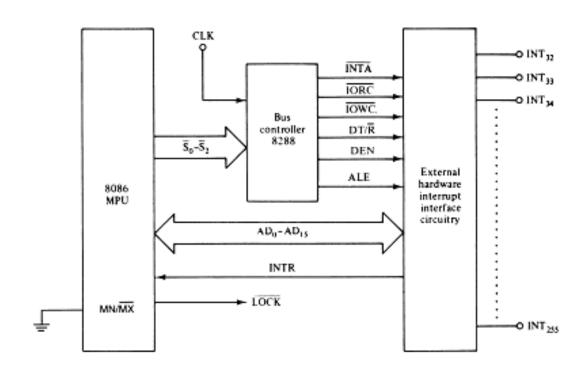

# ❖ Maximum-Mode Interrupt Interface

## **Memory Unit**

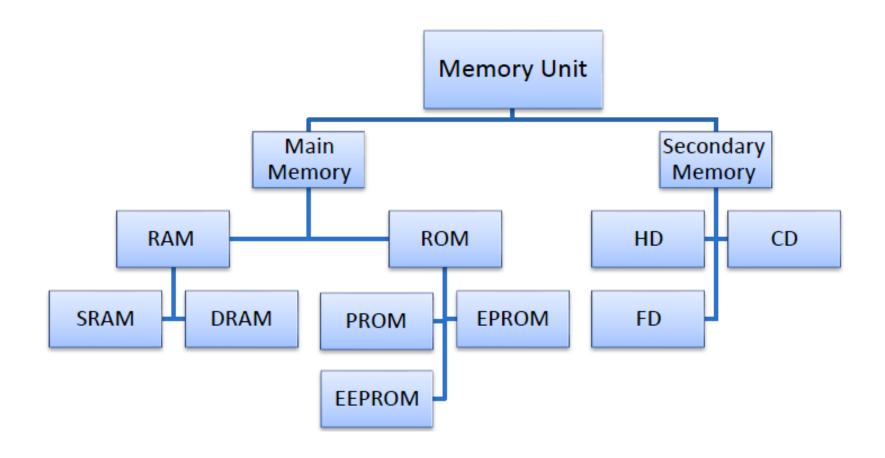

It is a collection of storage cells together with associated circuits needed to transfer information in and out of storage device. The memory stores binary information in groups of bits called bytes or words. The memory unit is mainly divided into two main parts:

- 1. Main Memory (Primary Memory)

- 2. Secondary storage devices (Magnetic Memory)

## **Main Memory (Primary Memory)**

Main memory (Semiconductor Memory) is faster, compact and lighter. It consumes less power supply. It is static device i.e. there is no rotating part in it. Semiconductor memory is employed as the Main Memory or Primary Memory of the computer. It stores the program, which are currently needed by the CPU. The main memory is divided into:

- 1. RAM (Random Access Memory)

- 2. ROM (Read Only Memory)

#### **RAM (Random Access Memory)**

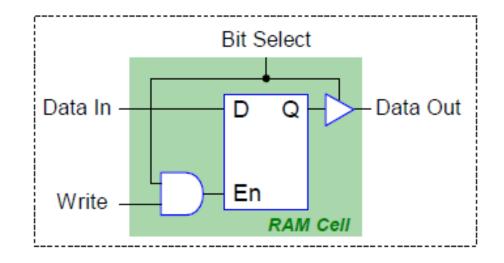

RAM stands for Random Access Memory. It is called volatile memory because it does not retain the data stored in it when the system's power is turned off. RAM provides space for your computer to read and write data to be accessed by the CPU (central processing unit). RAM can be both read and written, hold the programs, operating system, and data required by the system.

#### There are two main types of RAM:

➤ **DRAM (Dynamic RAM)** - each one-bit memory cell uses a capacitor for data storage and a transistor to access the cell. typically has access times of 50 to 70 nanoseconds(ns). DRAM is slower and less expensive than SRAM.

SRAM (Static RAM) - one-bit memory cells use bistable latches (flipflop) for data storage. It is faster with a typical assess time of 10 nanoseconds. It is more expensive and can only store a quarter of the data that DRAM is able to in the same given area, however data will remain stored as long as power is on. Fast SRAM can be found in most CPU's called cache memory.

# **ROM (Read Only Memory)**

ROM stands for Read-Only Memory. It refers to computer memory chips containing permanent or semi-permanent data. Unlike RAM, ROM is nonvolatile; even after you turn off your computer, the contents of ROM will remain. The types of ROM are:

- □ **Programmable read only memory (PROM)** are programmed during manufacturing process. The contents of each memory cell is locked by a fuse (diodes). PROMs are used for permanent data storage.

- □ Erasable Programmable read only memory (EPROM) there is a possibility to erase EPROM with ultraviolet light (about 20 minutes) what sets all bits in memory cells to 1. Programming requires higher voltage. Memory cells are built with floating gate transistors. Data can be stored in EPROMs for about 10 years.

□ Electrically erasable read only memory (EEPROM) - erasing does not require ultra-violet light but higher voltage and can be applied not to the whole circuit but to each memory cell separately.

# **Magnetic Memory**

The magnetic memory is cheaper than static memory. It is in the form of magnetic disks {hard disk (HD), compact disk (CD) and floppy disk}. It is used as secondary memory or Auxiliary memory. The size is in G-Bytes but the speed is very low compared with main memory.

# **Memory and Memory Address Decoding**

A memory device can be viewed as a single column table as shown below. Table index (row number) refers to the address of the memory. Table entries refer to the memory contents or data. Each table entry is referred as a memory location. Both the memory address and the memory contents are binary numbers, expressed in most cases in Hex format. The size of a memory device is specified as the number of memory locations. For example a 1Kbyte x 8 memory device has 1024 memory locations, with an width of 8 bits.

| Memory Address |            | <u>Memory</u>   |

|----------------|------------|-----------------|

| <u>Binary</u>  | <u>Hex</u> | <u>Contents</u> |

| 00-0000-0000   | 000        | 10011001        |

| 00-0000-0001   | 001        | 00111000        |

| 00-0000-0010   | 002        | 11001001        |

| 00-0000-0011   | 003        | 00111011        |

|                |            |                 |

| 11-1111-1100   | 3FC        | 01101000        |

| 11-1111-1101   | 3FD        | 10111001        |

| 11-1111-1110   | 3FE        | 00110100        |

| 11-1111-111    | 3FF        | 00011000        |

1024 X 8 (or 1KX8) Memory

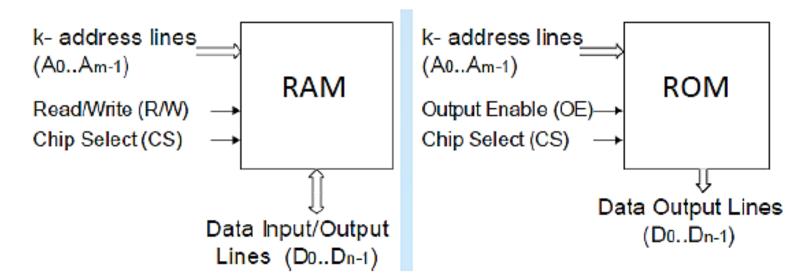

A memory device must have three types of lines or connections: Address, Data, and Enable & Control.

Address Lines: The input lines that select a memory location within the memory device. Decoders are used, inside the memory chip, to select a specific location. The number of address pins on a memory chip specifies the number of memory locations.

If a memory chip has 13 address pins  $(A_0 - A_{12})$ , then then the size is  $2^{13} = 2^3 \times 2^{10} = 8$  Kbyte.

If a memory chip has 4Kbytes, then it has N pins:

$$2^{N} = 4 \text{ Kbyte} = 2^{12} \rightarrow N = 12 \text{ address pins } (A_0 - A_{11})$$

- Data Connections: All memory devices have a set of data output pins (for ROM devices), or input/output pins (for RAM devices).

- Enable and Control Connections: All memory devices have at least one Chip Select CS or Chip Enable (CE) input, used to select or enable the memory device. If a device is not selected or enabled then no data can be read from, or written into it.

The CS or CE input is usually controlled by the microprocessor through the higher address lines via an address decoding circuit. RAM chips have two control input signals that specify the type of memory operation: the Read (RD) and the Write (WR) signals. ROM chips can perform only memory read operations, thus there is only read (RD) signal. In most real ROM devices the Read signal is called the Output Enable (OE) signal.

# Address Decoding

The physical address space, or memory map, of a microprocessor refers to the range of addresses of memory locations that can be accessed by the microprocessor. The size of the address space depends on the number of address lines of the microprocessor.

At least two memory devices are required in a microprocessor system: one for the ROM and one for the RAM. In an 8088/8086 the high addresses in the memory map should always be occupied by a ROM, while the low addresses in the memory map should always be occupied by a RAM.

Address decoding is required in order to enable the connection of more than one memory devices on the microprocessor. More than one memory devices can be used to expand (increase) the number of memory locations on the system. The following steps have to be followed to design a memory map:

1. Determine the number of memory chips required, by dividing the required memory size with the size of the memory devices to be used.

- Connect the data lines of each memory chip in parallel on the data lines of the processor.

- Connect the address lines of each memory chip in parallel with the low address lines of the processor.

- 4. Connect the CS lines of each memory device with the high address lines of the processor through an address decoding circuit..

- 5. Connect together all **WR** and **RD** lines of each memory device.

The following example is assumed that the processor has only 7 address lines  $(A_0 - A_6)$ , thus it can address  $2^7$ =128 memory locations. The data lines are 4  $(D_0 - D_3)$  The size of the RAM used in the system is 32 locations (4 chips of 8 locations), then 3 address lines  $(A_0 - A_2)$  are used to address the 8 locations of each RAM chip. There are 4 address lines  $(A_3 - A_6)$  used as chip select.

The memory block occupied by the memory module depends on the connection of the address selection circuit (AND gate) that enables the decoder.

Two address lines are used to control the address selection circuit, thus the circuit can be configured to occupy four different areas in the address space.